# 5V/12V Synchronous-Rectified Buck Controller

### General Description

The uP1513 is a compact synchronous-rectified buck controller specifically designed to operate from 5V or 12V supply voltage and to deliver high quality output voltage as low as 0.6V. This 8-pin device operates at fixed 300kHz frequency and provides an optimal level of integration to reduce size and cost of the power supply.

The uP1513 supports both tracking mode and stand-alone mode operation. The output voltage is tightly regulated to the external reference voltage from 0.4V to 3.0V at tracking mode or to internal 0.6V reference at stand-alone mode. The uP1513 integrates MOSFET drivers that support 12V+12V bootstrapped voltage for high efficiency power conversion. The bootstrap diode is built-in to simplify the circuit design and minimize external part count.

The uP1513 supports diode emulation mode operation that yields high efficiency over all the output current range. Besides, an OCP/EN is used for chip disable and continuous setting of over current protection level.

Other features include under voltage lockout (UVLO), internal softstart. With aforementioned functions, this part provides customers a compact, high efficiency, well-protected and cost-effective solutions. This part is available in PSOP-8 package.

# Applications

- Power Supplies for Microprocessors or Subsystem Power Supplies

- Cable Modems, Set Top Boxes, and xDSL Modems

- Industrial Power Supplies; General Purpose Supplies

- 5V or 12V Input DC-DC Regulators

- Low Voltage Distributed Power Supplies

# Ordering Information

| Order Number | Package Type | Remark   | Top Marking |

|--------------|--------------|----------|-------------|

| uP1513PSU8   | PSOP-8       | With PSM | uP1513P     |

Note: uPI products are compatible with the current IPC/ JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

#### **Features**

- Operate from 5V or 12V Supply Voltage

- 3.3V to 12V V<sub>IN</sub> Input Range

- 0.6V V<sub>REF</sub> with 1.0% Accuracy

- Output Range from V<sub>REF</sub> to 80% of V<sub>IN</sub>

- Support Tracking Mode and Stand Alone Mode Operation

- Simple Voltage-Mode PWM Control Design

- 300 kHz Fixed Frequency Oscillator

- Internal Compensation

- Fast Transient Response

- 0% to 80% Duty Cycle

- Internal Bootstrapped Gate Drivers

- Integrated Bootstrap Diode

- Adaptive Shoot-Through Protection

- Upper MOSFET Short-Circuit Protection

- Lossless, Programmable Overcurrent Protection

- Uses Lower MOSFET R<sub>DS(ON)</sub>

- Support Diode Emulation Mode Operation

- Internal Soft Start

- RoHS Compliant and Halogen Free

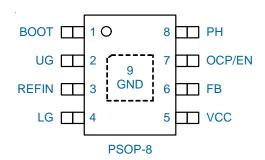

## . Pin Configuration

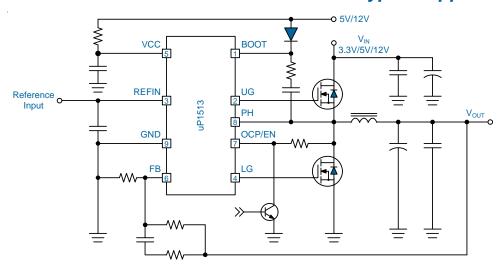

# Typical Application Circuit

# Functional Pin Description

| No. | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | воот      | <b>Bootstrap Supply</b> for the upper gate driver. Connect the bootstrap capacitor $C_{\text{BCOT}}$ between BOOT and PH pins to form a bootstrap circuit. The bootstrap capacitor provides the charge to turn on the upper MOSFET.                                                                                                                                                          |

| 2   | UG        | <b>Upper Gate Driver Output.</b> Connect this pin to the gate of upper MOSFET. This pin is monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off.                                                                                                                                                                                   |

| 3   | REFIN     | <b>External Reference Input for Tracking Mode Operation.</b> This pin receives a voltage with range from 0.4V to 3.0V as the reference voltage at the non-inverting input of the error amplifier. Pulling this pin lower than 0.3V disables the controller and causes the oscillator to stop, the UGATE and LGATE outputs to be held low. Let this pin open for internal 0.6V reference use. |

| 4   | LG        | <b>Lower Gate Driver Output.</b> Connect this pin to the gate of lower MOSFET. This pin is monitored by the adaptive shoot-through protection circuitry to determine when the lower MOSFET has turn off.                                                                                                                                                                                     |

| 5   | VCC       | <b>Supply Voltage.</b> This pin provides the bias supply for the uP1513 and the lower gate driver. The supply voltage is internally regulated to 4VDD for internal control circuit. Connect a well-decoupled 4.5V to 13.2V supply voltage to this pin. Ensure that a decoupling capacitor is placed near the IC.                                                                             |

| 6   | FB        | <b>Feedback Voltage.</b> This pin is the inverting input to the error amplifier. A resistor divider from the output to GND is used to set the regulation voltage.                                                                                                                                                                                                                            |

| 7   | OCP/EN    | <b>OCP Setting and Chip Enable.</b> Connect a resistor to PH pin to set the OCP level. Pulling this pin lower than 0.2V turns off the uP1513.                                                                                                                                                                                                                                                |

| 8   | PH        | <b>PHASE Switch Node.</b> Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET. This pin is used as the sink for the UG drive and is monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off.                                                                                                         |

| Exp | oosed Pad | <b>Ground.</b> The exposed pad should be well soldered to ground plane/island with lowest impedance for best thermal performance.                                                                                                                                                                                                                                                            |

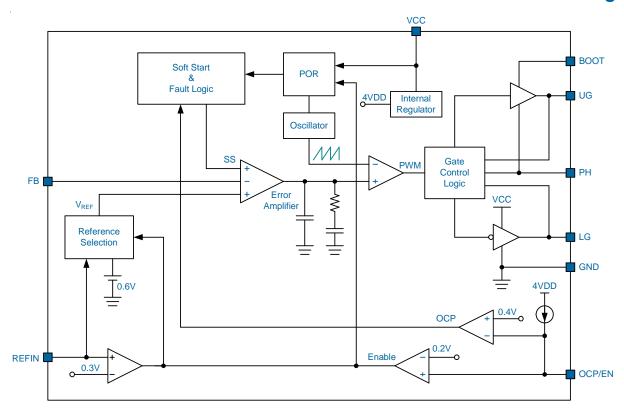

# Functional Block Diagram

## Functional Description

The uP1513 is a compact synchronous-rectified buck controller specifically designed to operate from 5V or 12V supply voltage and to deliver high quality output voltage as low as 0.8V. This 8-pin device operates at fixed 300kHz frequency and provides an optimal level of integration to reduce size and cost of the power supply.

The uP1513 integrates MOSFET drivers that support 12V+12V bootstrapped voltage for high efficiency power conversion. The bootstrap diode is built-in to simplify the circuit design and minimize external part count.

The uP1513 supports diode emulation mode operation that yields high efficiency over all the output current range. Besides, an OCP/EN is used for chip disable and continuous setting of over current protection level.

Other features include under voltage lockout (UVLO), internal softstart, under voltage protection, over voltage protection. With aforementioned functions, this part provides customers a compact, high efficiency, well-protected and cost-effective solutions. This part is available in SOP-8 or PSOP-8 packages.

### **Supply Voltage**

The VCC pin receives a well-decoupled 4.5V to 13.2V supply voltage to power the uP1513 control circuit, the lower gate driver and the bootstrap circuit for the higher gate driver. A minimum 0.1uF ceramic capacitor is recommended to bypass the supply voltage. Place the bypassing capacitor physically near the IC.

An internal linear regulator regulates supply voltage into a 4.0V voltage 4VDD for internal control logic circuit. No external bypass capacitor is required for filtering the 4VDD voltage.

The uP1513 integrates MOSFET gate drives that are powered from the VCC pin and support 12V+12V driving capability. A bootstrap diode is embedded to facilitate PCB design and reduce the total BOM cost. No external Schottky diode is required. Converters that consist of uP1513 feature high efficiency without special consideration on the selection of MOSFETs.

Note: The embedded bootstrap diode is not a Schottky diode having a 0.8V forward voltage. External Schottky diode is highly recommended if the VCC voltage is expected to be lower than 5.0V. Otherwise the bootstrap diode may be too low for the device to work normally.

#### **Power On Reset and Chip Enable**

A power on reset (POR) circuitry continuously monitors the supply voltage at VCC pin. Once the rising POR threshold is exceeded, the uP1513 sets itself to active state and is ready to accept chip enable command. The rising POR threshold is typically 4.2V at VCC rising.

The OCP/EN is a multi-functional pin: OCP level setting and chip enable. Pulling this pin by a small-signal transistor lower than 0.2V turns off the uP1513 as shown in the *Typical Application Circuit*. (Please refer to related sections for OCP setting.)

When released, an internal 40uA flows through the external circuit and pulls the  $V_{\rm OCP/EN}$  high. The uP1513 is enabled if the  $V_{\rm OCP/EN}$  is higher than 0.2V. Make sure  $V_{\rm OCP/EN}$  is always higher than 0.2V during normal operation.

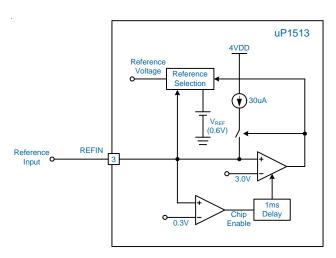

#### Tracking Mode and Stand Alone Mode Operation

The REFIN is a multifunctional pin: external reference input and chip enable as shown in Figure 1. *To Select Internal 0.6V Reference Voltage*, just let the REFIN open. A 30uA current source tries to pull high the REFIN voltage after POR that is monitored by the Enable Comparator monitors for chip enable. A signal level transistor is adequate to pull this pin down to ground and shut down the uP1513. As the REFIN voltage acrosses 0.3V threshold level, the Enable Comparator initiates the operation of the uP1513. The REFIN voltage is compared with 3.0V voltage to select the reference voltage with 1ms time delay after chip enabling. The internal 0.6V reference voltage is selected as the REFIN pulled high to internal 4VDD. The softstart cycle is initiated after reference selection is completed.

To Select External Reference Voltage, connect REFIN to a voltage source range from 0.4V to 3V. As the REFIN voltage acrosses 0.3V threshold level, the Enable Comparator initiates the operation of the uP1513. The REFIN voltage is compared with 3.0V voltage to select the reference voltage with 1ms time delay after chip enabling. The external reference input is selected as the REFIN voltage is lower than 3.0V. The 30uA current source is turn off if the external reference input is select to eliminate the load effect on the reference input. The softstart cycle is initiated after reference selection is completed.

Note that the 30uA current source will induces load effect on the external reference input and causes the REFIN voltage slightly higher than the external reference input during the reference selection. Make sure that the external reference input is strong enough so that REFIN voltage will not be higher than 3.0V.

## **Functional Description**

Figure 1. Reference Selection Function

#### **Soft Start**

A built-in Soft Start is used to prevent surge current from power supply input during turn on (referring to the Functional Block Diagram). The error amplifier is a three-input device. Reference voltage  $V_{\rm REF}$  or the internal soft start voltage SS whichever is smaller dominates the behavior of the non-inverting inputs of the error amplifier. SS internally ramps up to VDD with a fixed slew rate 1.5ms, no matter the VREF voltage.

The SS signal keeps ramping up after it exceeds the reference voltage  $V_{\text{REF}}.$  However, the reference voltage  $V_{\text{REF}}$  takes over the behavior of error amplifier after SS >  $V_{\text{REF}}.$  When the SS signal climb to 1.6 x  $V_{\text{REF}},$  the uP1513 claims the end of softstart cycle, enables the under voltage protection of the output voltage.

Figure 2. Softstart Behavior of uP1513

#### **Power Input Detection**

The uP1513 detects PH voltage for the present of power input when the UG turns on the first time. If the PH voltage does not exceed 3.0V when the UG turns on, the uP1513 asserts that power input in not ready and stops the softstart cycle. However, the internal SS continues ramping up to 4VDD. Another softstart is initiated after SS ramps up to 4VDD. The hiccup period is about 3ms.

Figure 3. Softstart where VIN does not Present Initially

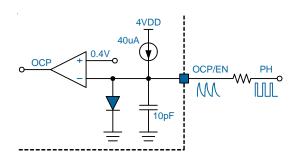

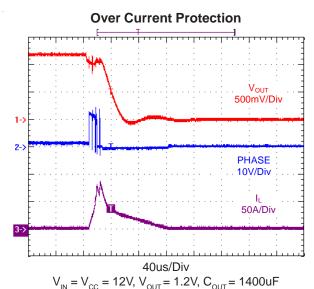

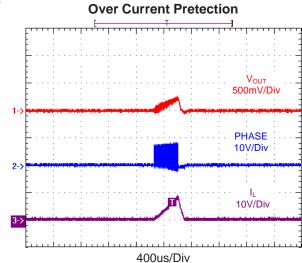

#### **Overcurrent Protection (OCP)**

A resistor connected from OCP/EN to PH node programs the over current protection level as shown in Figure 2. When the lower MOSFET turns on, the PH node voltage can be expressed as:

$$V_{PH} = -I_L \times R_{DS(ON)}$$

where  $I_L$  is the inductor current and  $R_{DS(ON)}$  is on-resistance of lower MOSFET.

Figure 4. Over Current Protection

Consequently, the stablized OCP/EN voltage  $\mathbf{V}_{\text{OCP/EN}}$  can be expressed as:

$$V_{OCP/EN} = 40uA \times R_{OCSET} - I_L \times R_{DS(ON)}$$

The OCP is triggered and turns off the uP1513 if  $V_{\rm OCP/EN}$

## **Functional Description**

is lower than 0.4V with about 5us time delay. The OCP level is calculated as:

$$I_{L\_OCP} = \frac{40uA \times R_{OCSET} - 0.4V}{R_{DS(ON)}}$$

Note that  $R_{OCSET}$  and parasitic capacitance to OCP/EN pin form a RC low-pass filter. Therefore, the OCP level is very sensitive to the RC time constant. Select external components so that external parasitic capacitance is lower than 10pF for accurate OCP level setting.

When programming the OCP level, take into consideration the conditions that affect  $R_{DS(ON)}$  of the lower MOSFET, including operation junction temperature, gate driving voltage and distribution. Consider the  $R_{DS(ON)}$  at maximum operation temperature and lowest gate driving voltage.

Another factor should taken into consideration is the ripple of the inductor current. The current near the valley of the ripple current is used for OCP, resulting the averaged OCP level a little higher than the calculated value.

Note: For application that uses unity feedback, no voltage divider could sink the IOCSET.A minimum load higher than 50uA is necessary to prevent abnormal output voltage.

#### **Diode Emulation Mode**

The uP1513 supports diode emulation mode that yields high efficiency at light load conditions.

The PH voltage is monitored for inductor zero current detection when the lower MOSFET turns on. When zero current crossing is detected, the uP1513 turns off lower MOSFET and runs the converter as conventional asynchronous buck converter, enabling discontinusous conduction mode operation (DCM). The converter will enter pulse skiping mode at extremely light load and yield high effeciency over all the output load conditions.

|                                                          | Absolute Maximum Rating                          |

|----------------------------------------------------------|--------------------------------------------------|

| Supply Input Voltage, VCC (Note 1)                       | 0.3V to +15V                                     |

| PH to GND                                                |                                                  |

| DC                                                       |                                                  |

| < 200ns                                                  |                                                  |

| BOOT to GND                                              |                                                  |

|                                                          |                                                  |

| < 200ns                                                  | 0.3V to 42V                                      |

| LG to GND                                                |                                                  |

|                                                          |                                                  |

|                                                          | 5V to 30V                                        |

| UG to PH                                                 |                                                  |

|                                                          |                                                  |

|                                                          |                                                  |

| Input, Output or I/O Voltage                             |                                                  |

| Storage Temperature Range                                |                                                  |

| Junction Temperature                                     |                                                  |

| Lead Temperature (Soldering, 10 sec)                     | 260°C                                            |

| ESD Rating (Note 2)                                      |                                                  |

| HBM (Human Body Mode)                                    | 2kV                                              |

| MM (Machine Mode)                                        | 200V                                             |

| •                                                        | Thermal Information                              |

|                                                          |                                                  |

| Package Thermal Resistance (Note 3)                      |                                                  |

| SOP-8 θ <sub>JA</sub>                                    |                                                  |

| PSOP-8 θ <sub>JA</sub>                                   |                                                  |

| SOP-8 θ <sub>JC</sub>                                    |                                                  |

| PSOP-8 $\theta_{\text{JC}}$                              | 5°C/W                                            |

| Power Dissipation, $P_D @ T_A = 25^{\circ}C$             |                                                  |

| SOP-8                                                    |                                                  |

| PSOP-8                                                   | 2.0W                                             |

|                                                          | Recommended Operation Conditions                 |

| Operating Junction Temperature Range (Note 4)            |                                                  |

| Operating Ambient Temperature Range                      |                                                  |

| Supply Input Voltage, V <sub>CC</sub>                    |                                                  |

|                                                          |                                                  |

| Note 1 Ctropped listed so the shows "Absolute Maximum De | stings" may say a parmonant domage to the daying |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}\text{C}$  on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 4. The device is not guaranteed to function outside its operating conditions.

# Electrical Characteristics

$(V_{CC} = 12V, T_A = 25^{O}C, unless otherwise specified)$

| Parameter                      | Symbol              | Test Conditions                                                                                      | Min   | Тур | Max   | Units            |

|--------------------------------|---------------------|------------------------------------------------------------------------------------------------------|-------|-----|-------|------------------|

| Supply Input                   |                     |                                                                                                      |       |     |       |                  |

| Supply Voltage                 | V <sub>CC</sub>     |                                                                                                      | 4.5   |     | 13.2  | V                |

| Supply Current                 | I <sub>cc</sub>     | UG, LG Open; Switching                                                                               |       | 2   |       | mA               |

| Quiescent Supply Current       | I <sub>CC_Q</sub>   | V <sub>FB</sub> = 0.9V, No Switching                                                                 |       | 1.5 |       | mA               |

| Power Input Voltage            | V <sub>IN</sub>     |                                                                                                      | 3.0   |     | 13.2  | V                |

| POR Threshold                  | V <sub>CCRTH</sub>  | V <sub>∞</sub> rising                                                                                | 4.0   | 4.2 | 4.4   | V                |

| POR Hysteresis                 | V <sub>CCHYS</sub>  |                                                                                                      |       | 0.5 |       | V                |

| Oscillator                     |                     |                                                                                                      |       |     |       |                  |

| Free Running Frequency         | f <sub>osc</sub>    |                                                                                                      | 270   | 300 | 330   | kHz              |

| Ramp Amplitude                 | $\Delta V_{OSC}$    | V <sub>N</sub> = 12V, V <sub>QUT</sub> = 1.2V                                                        |       | 3.0 |       | V <sub>P-P</sub> |

| Maximum Duty Cycle             |                     |                                                                                                      | 80    |     |       | %                |

| Minimum On Time                |                     |                                                                                                      |       | 200 |       | ns               |

| Reference Voltage              |                     |                                                                                                      | '     |     |       |                  |

| Nominal Feedback Voltage       | V <sub>FB</sub>     | Stand Alone Mode                                                                                     | 0.591 | 0.6 | 0.609 | V                |

| Output Voltage Accuracy        |                     | $\mid$ V <sub>FB</sub> - V <sub>REFIN</sub> $\mid$ , V <sub>REFIN</sub> = 0.4V ~ 1.0V, Tracking Mode |       |     | 15    | mV               |

|                                |                     | $ V_{\rm FB} - V_{\rm REFIN}  / V_{\rm REFIN} V_{\rm REFIN} = 1.0V \sim 3.0V$ , Tracking Mode        |       |     | 1.5   | %                |

| REFIN Enable Threshold         | V <sub>REFIN</sub>  |                                                                                                      |       | 0.3 | 0.35  | V                |

| Error Amplifier                |                     |                                                                                                      | '     |     |       |                  |

| Open Loop DC Gain              | AO                  | Guaranteed by Design                                                                                 | 55    | 70  |       | dB               |

| Gain-Bandwidth Product         | GBW                 | Guaranteed by Design                                                                                 |       | 10  |       | MHz              |

| Slew Rate                      | SR                  | Guaranteed by Design                                                                                 | 3     | 6   |       | V/us             |

| Transconductance               |                     | Guaranteed by Design                                                                                 |       |     | 0.2   | mS               |

| PWM Controller Gate Drivers    |                     |                                                                                                      |       |     |       |                  |

| Upper Gate Sourcing Resistance | R <sub>UG_SRC</sub> | I <sub>UG</sub> = 100mA sourcing                                                                     |       | 2   | 4     | Ω                |

| Upper Gate Sinking Resistance  | R <sub>UG_SNK</sub> | I <sub>UG</sub> = 100mA sinking                                                                      |       | 1   | 2     | Ω                |

| Lower Gate Sourcing Resistance | R <sub>LG_SRC</sub> | I <sub>LG</sub> = 100mA sourcing                                                                     |       | 1.5 | 3     | Ω                |

| Lower Gate Sinking Resistance  | R <sub>LG_SNK</sub> | I <sub>LG</sub> = 100mA sinking                                                                      |       | 1   | 4     | Ω                |

| PH Falling to LG Rising Delay  |                     | $V_{PH} < 1.2V \text{ to } V_{LG} > 1.2V$                                                            |       | 30  |       | ns               |

| LG Falling to UG Rising Delay  |                     | $V_{LG}$ < 1.2V to $(V_{UG} - V_{PH}) > 1.2V$                                                        |       | 30  |       | ns               |

# Electrical Characteristics

| Parameter                     | Symbol             | Test Conditions              | Min  | Тур  | Max  | Units |  |

|-------------------------------|--------------------|------------------------------|------|------|------|-------|--|

| OCP/EN                        |                    |                              |      |      |      |       |  |

| OCP/EN Current Source         | I <sub>OCSET</sub> | $V_{\text{CCP/EN}} = 0.5V.$  | 36   | 40   | 44   | uA    |  |

| Over Current Protection Level | $V_{CCP}$          |                              | 0.38 | 0.40 | 0.42 | V     |  |

| OCP Delay Time                |                    |                              |      | 5    |      | us    |  |

| Disable Threshold Level       | V <sub>DIS</sub>   | V <sub>CCP/EN</sub> falling. | 0.15 | 0.20 | 0.25 | V     |  |

| Disable Delay Time            |                    |                              |      | 5    |      | us    |  |

| Protection                    |                    |                              |      |      |      |       |  |

| Soft-Start Interval           | T <sub>SS</sub>    |                              | 1    | 1.5  | 2    | ms    |  |

| Zero Current Corsing          | V <sub>ZC</sub>    | V <sub>PH</sub> falling      | -2   | -1   | 0    | mV    |  |

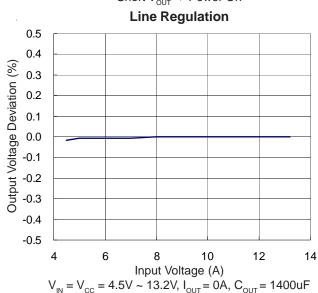

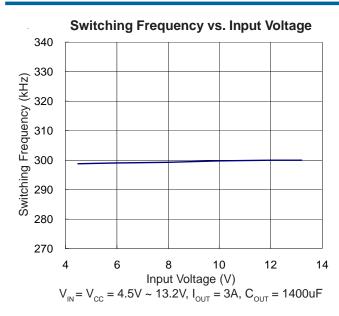

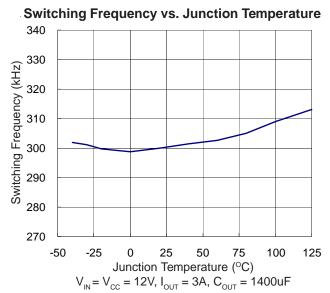

# **Typical Operation Characteristics**

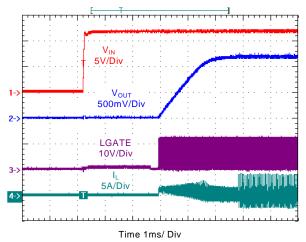

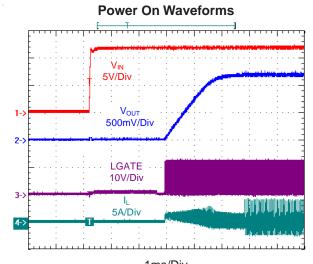

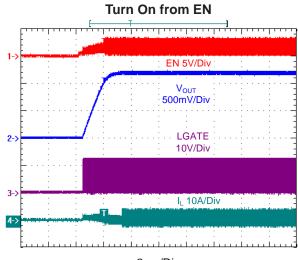

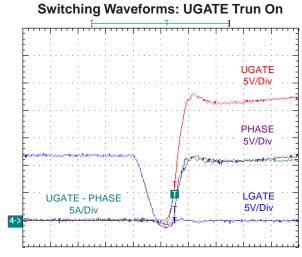

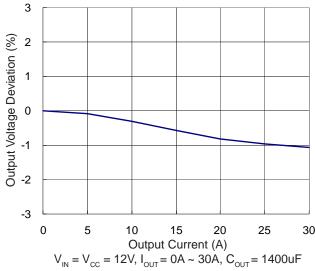

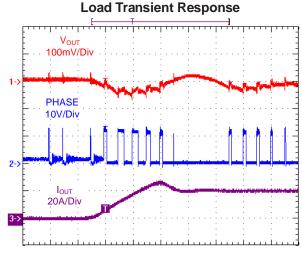

$$V_{IN} = V_{CC} = 12V, V_{OUT} = 1.2V, C_{OUT} = 1400uF, No Load$$

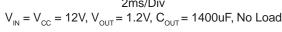

$V_{IN} = V_{CC} = 12V, I_{OUT} = 10A$

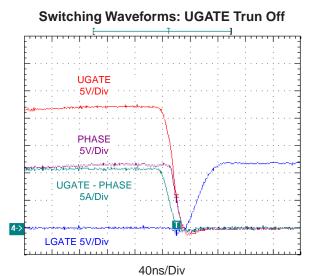

$$40 \text{ns/Div}$$

$$V_{IN} = V_{CC} = 12 \text{V}, I_{OUT} = 10 \text{A}$$

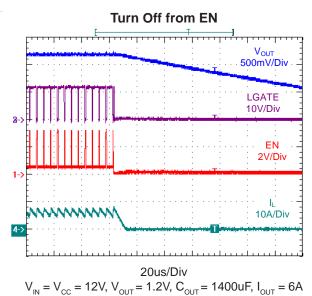

$$V_{IN} = V_{CC} = 12V, C_{OUT} = 1400uF, I_{OUT} = 6A$$

# **Typical Operation Characteristics**

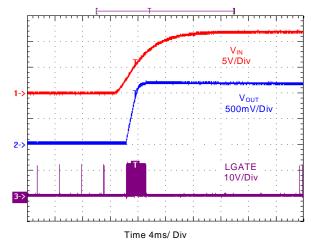

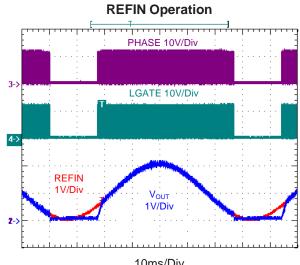

$$V_{IN} = V_{CC} = 12V, V_{OUT} = 1.2V, C_{OUT} = 1400uF, No Load$$

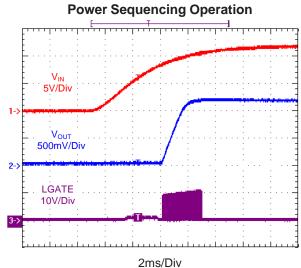

$V_{IN} = V_{CC} = 12V, V_{OUT} = 1.2V, C_{OUT} = 1400uF$ Short  $V_{OUT} \Rightarrow Power On$

# **Typical Operation Characteristics**

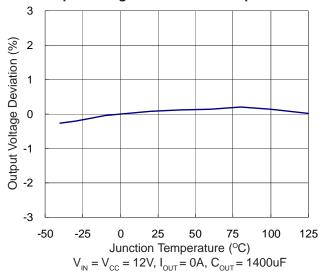

### **Output Voltage vs. Junction Temperature**

## Application Information

#### **Power MOSFET Selection**

External component selection is primarily determined by the maximum load current and begins with the selection of power MOSFET switches. The uP1513 requires two external N-channel power MOSFETs for upper (controlled) and lower (synchronous) switches. Important parameters for the power MOSFETs are the breakdown voltage  $V_{(BR)DSS}$ , on-resistance  $R_{DS(ON)}$ , reverse transfer capacitance  $C_{RSS}$ , maximum current  $I_{DS(MAX)}$ , gate supply requirements, and thermal management requirements.

The gate drive voltage is powered by VCC pin that receives  $4.5V\sim13.2V$  supply voltage. When operating with a 12V power supply for VCC (or down to a minimum supply voltage of 8V), a wide variety of NMOSFETs can be used. Logic-level threshold MOSFET should be used if the input voltage is expected to drop below 8V. Since the lower MOSFET is used as the current sensing element, particular attention must be paid to its on-resistance. Look for  $R_{DS(ON)}$  ratings at lowest gate driving voltage.

Special cautions should be exercised on the lower switch exhibiting very low threshold voltage  $V_{GS(TH)}$ . The shoot-through protection present aboard the uP1513 may be circumvented by these MOSFETs if they have large parasitic impedances and/or capacitances that would inhibit the gate of the MOSFET from being discharged below its threshold level before the complementary MOSFET is turned on. Also avoid MOSFETs with excessive switching times; the circuitry is expecting transitions to occur in under 50 nsec or so.

In high-current applications, the MOSFET power dissipation, package selection and heatsink are the dominant design factors. The power dissipation includes two loss components; conduction loss and switching loss. The conduction losses are the largest component of power dissipation for both the upper and the lower MOSFETs. These losses are distributed between the two MOSFETs according to duty cycle. Since the uP1513 is operating in continuous conduction mode, the duty cycles for the MOSFETs are:

$$D_{UP} = \frac{V_{OUT}}{V_{IN}} \quad D_{LO} = \frac{V_{IN} - V_{OUT}}{V_{IN}}$$

The resulting power dissipation in the MOSFETs at maximum output current are:

$$P_{UP} = I_{OUT}^2 \times R_{DS(ON)} \times D_{UP} + 0.5 \times I_{OUT} \times V_{IN} \times T_{SW} \times f_{OSC}$$

$$P_{LO} = I_{OUT}^2 \times R_{DS(ON)} \times D_{LO}$$

where T<sub>SW</sub> is the combined switch ON and OFF time.

Both MOSFETs have I<sup>2</sup>R losses and the top MOSFET includes an additional term for switching losses, which are largest at high input voltages. The bottom MOSFET losses reach the greatest when the bottom duty cycle is near 100%, during a short-circuit or at high input voltage. These equations assume linear voltage current transitions and do not adequately model power loss due the reverse-recovery of the lower MOSFET's body diode. Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal-resistance specifications. A separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air flow.

The gate-charge losses are dissipated by the uP1513 and don't heat the MOSFETs. However, large gate charge increases the switching interval,  $T_{SW}$  that increases the MOSFET switching losses. The gate-charge losses are calculated as:

$$P_G = V_{CC} \times (V_{CC} \times (C_{ISS\_UP} + C_{ISS\_LO}) + V_{IN} \times C_{RSS}) \times f_{OSC}$$

where  $C_{ISS\_UP}$  is the input capacitance of the upper MOSFET,  $C_{ISS\_LO}$  is the input capacitance of the lower MOSFET, and  $C_{RSS\_UP}$  is the reverse transfer capacitance of the upper MOSFET. Make sure that the gate-charge loss will not cause over temperature at uP1513, especially with large gate capacitance and high supply voltage.

#### **Output Inductor Selection**

Output inductor selection usually is based on the considerations of inductance, rated current, size requirement, and DC resistance (DC)

Given the desired input and output voltages, the inductor value and operating frequency determine the ripple current:

$$\Delta I_{L} = \frac{1}{f_{OSC} \times L_{OUT}} \times V_{OUT} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

Lower ripple current reduces core losses in the inductor, ESR losses in the output capacitors and output voltage ripple. Highest efficiency operation is obtained at low frequency with small ripple current. However, achieving this requires a large inductor. There is a tradeoff between component size, efficiency and operating frequency. A reasonable starting point is to choose a ripple current that is about 40% of I<sub>OUT(MAX)</sub>.

There is another tradeoff between output ripple current/voltage and response time to a transient load. Increasing the value of inductance reduces the output ripple current and voltage. However, the large inductance values reduce the converter's response time to a load transient.

## Application Information

Maximum current ratings of the inductor are generally specified in two methods: permissible DC current and saturation current. Permissible DC current is the allowable DC current that causes 40°C temperature raise. The saturation current is the allowable current that causes 10% inductance loss. Make sure that the inductor will not saturate over the operation conditions including temperature range, input voltage range, and maximum output current.

The size requirements refer to the area and height requirement for a particular design. For better efficiency, choose a low DC resistance inductor. DCR is usually inversely proportional to size.

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. The choice of which style inductor to use often depends more on the price vs. size requirements and any radiated field/EMI requirements.

### **Input Capacitor Selection**

The synchronous-rectified buck converter draws pulsed current with sharp edges from the input capacitor resulting in ripples and spikes at the input supply voltage. Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high frequency decoupling and bulk capacitors to supply the current needed each time upper MOSFET turns on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of upper MOSET and the source of lower MOSFET to avoid the stray inductance along the connection trace.

The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select the bulk capacitor with voltage and current ratings above the maximum input voltage and largest RMS

current required by the circuit. The capacitor voltage rating should be at least 1.25 times greater than the maximum input voltage and a voltage rating of 1.5 times is a conservative guideline. The RMS current rating requirement for the input capacitor of a buck converter is calculated as:

$$I_{IN(RMS)} = I_{OUT(MAX)} \frac{\sqrt{V_{OUT}(V_{IN} - V_{OUT})}}{V_{IN}}$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{IN(RMS)} = I_{OUT(RMS)}/2$ . This simple worst-case condition is commonly used for design because even significant

deviations do not offer much relief. Note that the capacitor manufacturer's ripple current ratings are often based on 2000 hours of life. This makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required. Always consult the manufacturer if there is any question.

For a through-hole design, several electrolytic capacitors may be needed. For surface mount designs, solid tantalum capacitors can also be used, but caution must be exercised with regard to the capacitor surge current rating. These capacitors must be capable of handling the surge-current at power-up. Some capacitor series available from reputable manufacturers are surge current tested.

#### **Output Capacitor Selection**

An output capacitor is required to filter the output and supply the load transient current. The selection of  $C_{OUT}$  is primarily determined by the ESR required to minimize voltage ripple and load step transients. The output ripple  $\Delta V_{OUT}$  is approximately bounded by:

$$\Delta V_{OUT} \leq \Delta I_L \big( \text{ESR} + \frac{1}{8 \times f_{OSC} \times C_{OUT}} \big)$$

Since ΔIL increases with input voltage, the output ripple is highest at maximum input voltage. Typically, once the ESR requirement is satisfied, the capacitance is adequate for filtering and has the necessary RMS current rating. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements. Dry tantalum, special polymer, aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Special polymer capacitors offer very low ESR but have lower capacitance density than other types.

The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitors and careful layout. Modern components and loads are capable of producing transient load rates above 1A/ns. High frequency capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR (Effective Series Resistance) and voltage rating requirements rather than actual capacitance requirements.

High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements.

## Application Information

Use only specialized low-ESR capacitors intended for switching-regulator applications for the bulk capacitors. The bulk capacitor's ESR will determine the output ripple voltage and the initial voltage drop after a high slew-rate transient. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes.

However, the Equivalent Series Inductance (ESL) of these capacitors increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading.

Unfortunately, ESL is not a specified parameter. Work with your capacitor supplier and measure the capacitor's impedance with frequency to select a suitable component. In most cases, multiple electrolytic capacitors of small case size perform better than a single large case capacitor.

#### **Bootstrap Capacitor Selection**

An external bootstrap capacitor  $C_{BOOT}$  connected to the BOOT pin supplies the gate drive voltage for the upper MOSFET. This capacitor is charged through the internal diode when the PHASE node is low. When the upper MOSFET turns on, the PHASE node rises to  $V_{IN}$  and the BOOT pin rises to approximately  $V_{IN} + V_{CC}$ . The boot capacitor needs to store about 100 times the gate charge required by the upper MOSFET. In most applications 0.1uF to 0.47uF, X5R or X7R dielectric capacitor is adequate.

### **PCB Layout Considerations**

High speed switching and relatively large peak currents in a synchronous-rectified buck converter make the PCB layout a very important part of design. Fast current switching from one device to another in a synchronous-rectified buck converter causes voltage spikes across the interconnecting impedances and parasitic circuit elements. The voltage spikes can degrade efficiency and radiate noise that result in overvoltage stress on devices. Careful component placement layout and printed circuit design minimizes the voltage spikes induced in the converter.

Follow the layout guidelines for optimal performance of uP1513

1 The upper and lower MOSFETs turn on/off and conduct pulsed current alternatively with high slew rate transition. Any inductance in the switched current path generates a large voltage spike during the switching. The interconnecting wires indicated by red heavy lines conduct pulsed current with sharp transient and should be part of a ground or power plane in a printed circuit board to minimize the voltage spike. Make all the connection the top layer with wide, copper filled areas.

- Place the power components as physically close as possible.

- 2.1 Place the input capacitors, especially the high-frequency ceramic decoupling capacitors, directly to the drain of upper MOSFET ad the source of the lower MOSFET. To reduce the ESR replace the single input capacitor with two parallel units

- 2.2 Place the output capacitor between the converter and load.

- 3 Place the uP1513 near the upper and lower MOSFETs with pins 1 to 4 facing the power components. Keep the components connected to pins 4 to 8 close to the uP1513 and away from the inductor and other noise sources (noise sensitive components).

- 4 Use a dedicated grounding plane and use vias to ground all critical components to this layer. The ground plane layer should not have any traces and it should be as close as possible to the layer with power MOSFETs. Use an immediate via to connect the components to ground plane including GND of uP1513 Use several bigger vias for power components.

- 5 Apply another solid layer as a power plane and cut this plane into smaller islands of common voltage levels. The power plane should support the input power and output power nodes to maintain good voltage filtering and to keep power losses low. Also, for higher currents, it is recommended to use a multilayer board to help with heat sinking power components.

- The PHASE node is subject to very high dV/dt voltages. Stray capacitance between this island and the surrounding circuitry tend to induce current spike and capacitive noise coupling. Keep the sensitive circuit away from the PHASE node and keep the PCB area small to limit the capacitive coupling. However, the PCB area should be kept moderate since it also acts as main heat convection path of the lower MOSFET.

- 7 uP1513 sources/sinks impulse current with 2A peak to turn on/off the upper and lower MOSFETs. The connecting trance between the controller and gate/ source of the MOSFET should be wide and short to minimize the parasitic inductance along the traces.

- 8 Flood all unused areas on all layers with copper. Flooding with copper will reduce the temperature rise of power component.

- 9 Provide local VCC decoupling between VCC and GND pins. Locate the capacitor, C<sub>BOOT</sub> as close as practical to the BOOT and PH pins.

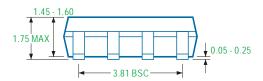

## . Package Information

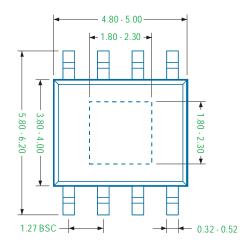

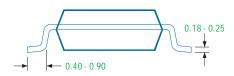

#### PSOP-8L Package

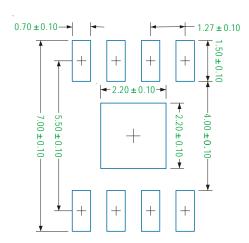

#### Recommended Solder Pad Layout

#### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions no not include mold flash or protrusions. Mold flash or protrusions shell not exceed 0.15mm.